Ethernet Switch Evolution: High Speed Interfaces

Technology development has always been driven by emerging applications: big data, Internet of Things, machine learning, public and private clouds, augmented reality, 800G Ethernet, etc.

Merchant Silicon switch ASIC chip development is an excellent example of that golden rule.

OIF’s Common Electrical Interface Development

The Optical Internetworking Forum (OIF) is the standards body – a nonprofit industry organization – that develops common electrical interfaces (CEIs) for next-generation technology to ensure component and system interoperability.

The organization develops and promotes implementation agreements (IAs), offering principal design and deployment guidance for a SerDes (serializer-deserializer), including:

- CEI-6G (which specifies the transmitter, receiver and interconnect channel associated with 6+ Gbps interfaces)

- CEI-11G (which specifies the transmitter, receiver and interconnect channel associated with 11+ Gbps interfaces)

- CEI-28G (which specifies the transmitter, receiver and interconnect channel associated with 28+ Gbps interfaces)

- CEI-56G (which specifies the transmitter, receiver and interconnect channel associated with 56+ Gbps interfaces)

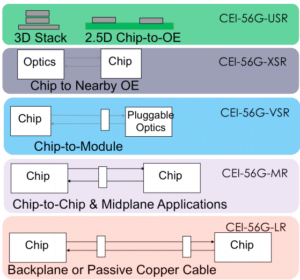

OIF’s CEI specifications are developed for different electrical interconnect reaches and applications to ensure system service and connectivity interoperability at the physical level:

- USR: Ultra-short reach, for < 10 mm die to optical engine within a multi-chip module (MCM) package.

- XSR: Extremely short reach, for < 50 mm chip to nearby optical engine (mid-board optics); or CPU to CPU/DSP arrays/memory stack with high-speed SerDes.

- VSR: Very short reach, < 30 cm chip (e.g. switch chip) to module (edge pluggable cage, such as SFP+, QSFP+, QSFP-DD, OSFP, etc.).

Read full article